## 2110 DIAG0

Page Control Register (PCREG) A12U860 (schematic diagram 1):

## Testing Method:

Sets PCREG (bit D7) = 0 and tests for = 0 (stuck at one). Sets PCREG (bit D7) = 1 and tests for = 1 (stuck at zero). If both tests pass, the result flag is set to PASS; otherwise, it is set to FAIL.

If test = FAIL then look for failure using the following steps:

On the test scope, connect CH 1 to J125 pin 15. Select Slope, + (plus); Trigger Source, CH 1;

Trigger Level, 1 V; CH 1 and CH 2 input coupling, DC; CH 1 and CH 2 VOLTS/DIV, 2 V. This

step provides a positive, TTL-level trigger strobe (or pulse) for validation of the signal being tested

while a test is running. The test scope setup will be used in each of the Registers troubleshooting

procedures.

# Now using CH2 probe:

- Run test 2110 in CONTINUOUS mode and check for clock activity at U860 pin 11 (clocks on LOto-HI transition close to the end of the trigger strobe pulse); if not, troubleshoot its clocking circuitry (U884, U862, and U866).

- Check that U860 pin 19 clocks from LO-to-HI and remains HI after the trigger strobe pulse returns to LO. If not, replace U860.

- 4. Test for a chip select at U854 pins 1 and 19 (LO enables). If not correct, troubleshoot System Address Decode circuitry (U884, U862, and U866).

- 5. While selected, check that U854 pin 11 is set to the state of U860 pin 19. If DIAG0 failed and the chip selects to U854 and the signal to U854 pin 11 are ok, then U854 is probably defective.

## 2120 DCOK U654

Interrupt Register A12U654 (schematic diagram 1) and DCOK logic circuitry A16U395 and associated components (schematic diagram 23):

## Testing Method:

The power supply sends a TTL signal to the interrupt register to inform the System  $\mu P$  of the logic AND of the power supply voltages. DCOK tests INTREG (bit 7). If = 1, the test result = PASS; otherwise, the result = FAIL.

# Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

#### Now using CH2 probe:

- Run test 2120 in CONTINUOUS MODE and check for INTREG chip select on pins 1 and 19 of Interrupt Register U654. If not present, troubleshoot the System Address Decoding circuitry (U884, U862, U866A, U870B, and associated components) for proper inputs and outputs.

- 3. While the test is running, test U654 pin 17 for steady-state HI value. If HI and DCOK fails, then replace U654. If LO, then check the power supply voltages and the DCOK AND circuit. If supply voltages are not correct, troubleshoot the low-voltage power supply and regulators; if voltages are correct, troubleshoot A16U395 and associated components (schematic diagram 23).

### 2130 BUSTAKE

Page Control Register A12U860 (schematic diagram 1), OR-gate A12U332D (schematic diagram 2), and Interrupt Register A12U654:

#### Testing Method:

To test for stuck at 1, PCREG U860 is written the pattern x00xxxxx to clear BUS REQUEST and BUSTAKE bits. Then INTREG (bit 6) is tested for = 0, and the PASS/FAIL results are set accordingly.

The PCREG is set for a BUSTAKE (x1xxxxxx). This time the INTREG (bit 6) should = 1. The result is set to FAIL if the test fails.

### Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- Run test 2130 in CONTINUOUS MODE and check for NTREG chip select at U654 pin 1 and 19. If not present, troubleshoot the System Address Decoding circuitry (U884, U862, U866A, U870B, and associated components) for proper inputs and outputs.

- 3. Check that BUSTAKE on PCREG U860 pin 16 has LO-to-HI and HI-to-LO transitions on alternate PCREG chip selects. If not, suspect problem with U860.

- 4. Check INTREG U654 pin 15 for a LO-to-HI transition when BUSTAKE on PCREG U860 pin 16 is set from LO-to-HI; if not, then check U332D (schematic diagram 2) for correct gating.

## 2140 DIAG1

Processor Miscellaneous Out and Processor Miscellaneous In Registers (A12U750 and A12U854) Diagnostic Bit 1 (schematic diagram 1):

#### Testing Method:

This is the first test for the PMISCOUT and PMISCIN registers. The byte to PMISCOUT U760 is set to 00000000 and PMISCIN (bit 4) is tested for = 0. The test result flag is set PASS or FAIL. PMISCOUT is then set to 10000000 and PMISCIN (bit 4) is again tested. If the test fails, the test result is set to FAIL.

# Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 2. Run test 2140 in CONTINUOUS MODE and check for chip select at U760 pin 11. If not present, troubleshoot the System Address Decoding circuitry (U884, U862, U866A, U870B, and associated components) for proper inputs and outputs.

- Test U760 pin 19 for a LO-to-HI transition between chip selects. If missing, replace U760; if ok, suspect U854.

## 2150 COMREG

Interrupt Latch (COMREG) A12U550 and Display Status Register (SSREG) A12U542 (schematic diagram 2):

## Testing Method:

A BUSTAKE is executed (previously tested) and the 4Q output of U550 (pin 15) is set LO. SSREG U542 bits 0 and 1 (pins 16 and 18) are then tested to see if they are LO, and the test results are set accordingly.

#### NOTE

The inputs of U542 (pins 2 and 4) are wired together.

Pin 15 of U550 is then set HI and SSREG bits 0 and 1 are tested for HI. If the test fails, the test result is set to FAIL.

## Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

### Now using CH 2 probe:

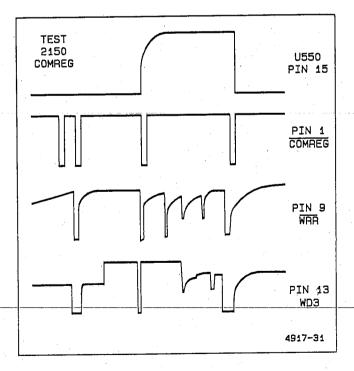

2. Run test 2150 in CONTINUOUS mode and check that U550 pin 1 (COMREG) is set LO during the period that the clock line (WWR) to U550 at pin 9 has a LO-to-HI transition. This may be done by saving the COMREG signal in REF1 and displaying it at the same time as the clock pulse on U550 pin 9 is acquired. If these signals are not coincident, then troubleshoot the cause and correct the problem. See Figure 6-8 for typical register test waveforms.

Figure 6-8. Typical Register test waveforms.

3. Check that U550 pin 15 has a LO-to-HI transition after the second clock pulse goes LO-to-HI. If no transition, change U550; if ok, check chip enable of U542 on pin 1 (SSREG) to be LO after WRR on U550 pin 9 goes LO-to-HI. If ok, then suspect U550. If the enable is defective, trouble-shoot and correct the problem.

### 2160 WPDN

Waveform μP Done A12U550 (schematic diagram 2):

Testing Method:

A BUSTAKE is executed (previously tested) and pin 10 of Interrupt Latch U550 is set LO. Then pin 14 (bit 2) of PMISCIN register U854 (schematic diagram 1) is tested for a LO, and the test results are set accordingly.

Then pin 10 of U550 is set HI, and U854 pin 14 is tested for a HI. If test fails, the test result is set to FAIL.

Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using CH2 probe:

- 2. Run test 2160 in CONTINUOUS mode and check that U550 pin 1 (COMREG) is set LO during the period that the clock to U550 pin 9 (WRR) has a LO-to-HI transition. This may be done by saving the COMREG signal in REF1 and displaying while acquiring the clock pulse on U550 pin 9. If these signals are not coincident, then troubleshoot the cause.

- 3. Check that U550 pin 10 has a HI-to-LO transition on the first enable and a LO-to-HI transition after the second clock pulse goes LO-to-HI. If bad, change U550; if good, check chip enable at U854 pins 1 and 19 is LO after U550 pin 10 goes from LO-to-HI. If ok, then suspect U854. If the enable is defective, troubleshoot and correct the problem.

#### 2170 DIAG2

Diagnostic Bit 2 Word Trigger Register A12U754 (diagram 20):

Testing Method

WDREG U754 pin 19 (DIAG2) is set to 0xxxxxxx and PMISCIN A12U854 pin 5 (bit D6) (schematic diagram 1) is tested for 0. The test result is to PASS or FAIL accordingly.

WDREG U754 pin 19 (DIAG2) is then set to 1xxxxxxx and PMISCIN U854 pin 5 (bit D6) is tested for 1. If the test fails, the test result is set to FAIL.

WDREG also drives the GPIB LEDS on the front panel. Bit patterns xxxxx000 to xxxxx111 are sent in a binary sequence with a 50 ms delay between patterns. The register is then reset to entry values.

Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using CH2 probe:

- 2. Check that U754 pin 1 RESET is HI.

- 3. Run test 2170 in CONTINUOUS mode and check the clock line to A12U754 at pin 11 for LO-to-HI transitions. Since this is the register that provides the strobe to WORD TRIG, there should be four clock pulses, one at each end of the trigger strobe and two under it. If not, troubleshoot the clock source to isolate the problem.

- 4. Test that U754 pin 19 has a LO-to-HI transition on the third strobe. If there is no LO-to-HI transition, replace U754. If there is, then test A12U854 pin 15 for the same signal as at U759 pin 19. If present, replace U854; if not, find the open.

2180 FLD2 -Video-Option-Mode Register A12U750 (schematic diagram 20):

Testing Method:

TVREG U750 is set = 00000000 and PMISCIN A12U750 pin 3 (schematic diagram 1) is tested for 0. The test result is set accordingly.

TVREG U750 pin 2 (bit D0) is then set to 1 and PMISCIN (bit D7) is tested. If the test fails, the test result is set to FAIL.

Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- Run test 2180 in CONTINUOUS mode and check the clock line to A12U750 TVREG, pin 11 (schematic diagram 20) for LO-to-HI transitions. There should be two clock pulses under the trigger strobe. If not, troubleshoot the clock source back through Decoder A12U884 (schematic diagram 1) to isolate the problem.

- Test that U750 pin 2 (FLD2) has a LO-to-HI transition on the second strobe. If there is no LO-to-HI transition, replace U750. If there is, then test U854 pin 17 (schematic diagram 1) for the same signal as at U750 pin 2. If present, replace U854; if not, find the open.

2190 MWPDN Miscellaneous Register A12U760 (schematic diagram 1):

Testing Method:

A BUSTAKE is executed (previously tested), Interrupt Latch bit D2 is set true (WPDN) and PMISCOUT Register U760 pin 2 (the mask for WPDN), is set to 0.

INTREG U654 pin 18 (bit D0) is tested for 0 and the test result is set accordingly.

PMISCOUT U760 pin 2 (bit D0) is set to 1 which should unmask the WPDN that is already set true. INTREG (bit 0) is tested for 1. If test fails, the test result is set to FAIL.

Troubleshooting Procedure:

If test = FAIL then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 2. Run test 2190 in CONTINUOUS mode and check that A12U550 pin 1 COMREG (schematic diagram 2) is set LO during the period that the clock line U550 pin 9 has a LO-to-HI transition. This may be done by saving the COMREG signal in REF1 (if using a 2440 as the test scope) and displaying it while acquiring the clock pulse on U550 pin 9. If these signals are not coincident, then troubleshoot the cause.

- Check that U550 pin 2 has a LO-to-HI transition on the second clock pulse. If bad, change U550.

If ok, store in REF1 and display it while testing output of A12U880 pin 6 (schematic diagram 1). If

ok then replace U654; if not, check the inputs to U880 on pins 4 and 5, and if those are ok,

replace U880.

### 2200 TB-DSP

Display Control Registers (schematic diagram 17):

Testing Method:

Running the test from this level will test all the Display Control registers. These tests will utilize four bit patterns to detect faults. If marked FAIL at this level, go to the lower levels in the menu to test for the failed register. The four bit patterns sent in each of the register tests are as follows:

Test 1—10100101 is sent to the input latch and read back via the output buffer. Test result is set to fail if not a match.

Test 2-01001011 is sent and read back. Test result is set to fail if not a match.

Test 3-10010110 is sent read back. Test result is set to fail if not a match.

Test 4-00101101 is sent and read back. Test result is set to fail if not a match.

#### NOTE

DISCON (bit 0) will not change, as it has the main board diagnostics as its input.

#### 2210 MISC

Misc Registers A11U532 and A11U540 (schematic diagram 17):

Testing Method:

The MISC register is two components; latch U532 and read-back buffer U540. The test result is set to PASS and the test is done; any failure sets it to FAIL.

If run from this level, all four tests are selected in turn. One may execute any single test by selecting 2211 to 2214. The test involves writing four unique patterns (see test 2200) to U532 and reading them back from U540. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test fails and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

Troubleshooting Procedure:

If test = FAIL for all tests, then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- Run test 2210 in CONTINUOUS Mode and check U532 pin 1 for MISC to be LO during the time

of the trigger strobe. If not, troubleshoot the Register Select circuitry (U550 and U450D) for proper

operation.

- 3. Check U532 pin 19 for clock pulse activity  $\overline{\text{(WR)}}$  strobe from System  $\mu\text{P}$ ).

- 4. If 1 and 2 above are ok, then select a pattern test and check that the data lines are the same states as the pattern; i.e., 10100101 would have the D7 pin = 1, D6 pin = 0, etc.

#### NOTE

Must select test mode of RUN ONCE for stability.

If ok, repeat steps 2 and 3 for U540, and replace U540 if steps 2 and 3 pass.

## 2220 MODECON

Mode Control Register A11U541 and A11U542 (schematic diagram 17):

Testing Method:

The MODECON register is two components, latch U541 and read-back buffer U542. The test result is set to PASS, any failure sets it to FAIL.

If run from this level, all four tests are selected in turn. One may execute any one test by selecting 2221 to 2224. The test involves writing four unique patterns (see test 2200) to U541 and reading them back from U542. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test fails and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

Troubleshooting Procedure:

If test = FAIL for all test then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- Check U541 pin 1 for PWRUP = HI; if not, troubleshoot Power Up circuitry (schematic diagram 23).

- 3. Run test 2220 in CONTINUOUS mode and check U541 pin 11 for clock pulse MODECON activity.

#### NOTE

First clock pulse is the write to U541, the second is the read from U542.

4. If 2 and 3 above are ok, then select a pattern test and check that the data lines are the same states as the pattern; i.e., 10100101 would have the D7 pin = 1, D6 pin = 0, etc. If ok, replace U542.

## 2230 DISCON

Display Control Register A11U530 and A11U531 (schematic diagram 17):

Testing Method:

The DISCON (display control) register is two components, latch U530 and read-back buffer U531. The test result is set to PASS, any failure sets it to FAIL.

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2231 to 2234. The test involves writing four unique patterns (see test 2200) to U530 and reading them back from U531. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test fails and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

### NOTE

The readback bit (bit 0) is the main board diagnostic bit and will not be tested.

Troubleshooting Procedure:

If test = FAIL for all test then look for failure using the following steps:

1. Set up the test scope as per Step 1 of the 2110 troubleshooting procedure.

Using the CH 2 probe:

- Run test 2230 in CONTINUOUS mode and check U530 pin 1 for DISCON = LO during the time of the trigger strobe. If not, troubleshoot the Register Select circuit (U550 and U450D) for proper operation.

- 3. Check U530 pin 11 for clock pulse activity  $\overline{\text{(WR)}}$  strobe from System  $\mu\text{P}$ ).

- 4. If 2 and 3 above are ok, then select a pattern test and check that the data lines are the same states as the pattern; i.e., 10100101 would have the D7 pin = 1, D6 pin = 0, etc. If ok, replace U531.

### 2300 TB-DSP

Display Memory Bus Registers:

Running this test will test all the Display bus registers. There are seven tests in this section. The first two write a pattern to one register and read back from another as in the previous section.

The next three tests deal with the "Q" bus of the display state machine and require strobing of data and shifting of bits for readout.

The remaining two tests use initialized data in U441 and U440 (display and readout memory will be written with our standard four patterns in the first four bites of each memory).

If marked FAIL in the Extended Diagnostic menu, go to the next lower level of diagnostics and run those tests to determine the problem register.

# 2310 VCURS

Volts Cursors Register A11U241 (schematic diagram 16) Testing Method:

The Volts Cursors Register test checks two components; latch U241 readback is via Diagnostic Buffer U141. The test result is set to PASS, any failure sets it to FAIL.

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2311 to 2314. The test involves writing four unique patterns (see test 2200) to U241 and reading them back from U141. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test fails and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

# Troubleshooting Procedure:

If test = FAIL for all tests then look for failure using the following steps:

- Check U241 pin 1 to be LO (VCURSEN).

- 2. Check VCURS clock to U241 at pin 11 for activity (save to REF1 and display for timing).

- 3. Select one pattern and check each output relative to the REF1 clock pulse for the proper level for that bit/pattern. If incorrect, replace U241.

- 4. Check U141 pins 1 and 19 for the YDIAG pulse after the clock pulse to U241. If ok, replace U141. If not present, replace U550 (schematic diagram 17).

# 2320 TCURS

Time Cursor Register A11U441 (schematic diagram 16):

## Testing Method:

The TCURS test checks two ICs; U441 is a latch and the read back is Diagnostic Buffer U243. The test result is set to PASS, any failure sets it to FAIL.

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2321 to 2324. The test involves writing four unique patterns (see test 2200) to U441 and reading them back from U243. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test fails and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

# Troubleshooting Procedure:

If test = FAIL for all test then look for failure using the following steps:

- 1. Check U441 pin 1 to be LO (TCURSEN).

- 2. Check U441 pin 11 (TCURS) for clock activity (save to REF1 and display for timing).

- 3. Select one pattern and check each output relative to the REF1 clock pulse for the proper level for that bit/pattern. If incorrect, replace U441.

- Check U243 pins 1 and 19 for the XDIAG pulse after clock pulse to U441. If ok, replace U243; if not present, replace U550 (schematic diagram 17).

2330 U130 Ramp Buffer A11U130 (schematic diagram 16):

Testing Method:

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2331 to 2334.

This test requires the display state machine to be operative. There is no "good" way to ensure that it is functional, and there have been no previous tests to help to find that out. Therefore, if this test fails, it could be for several reasons other than U130. If the power-on Self Test starts to run but halts at test level 3000 or test level 6000 (as indicated by the lighted Trigger LEDs), the problem may be in the Display State Machine circuit (schematic diagram 17) or the DISDN signal path to the System  $\mu P$  Interrupt circuit. Use the Display Troubleshooting Chart to troubleshoot the Display State Machine and check that the DISDN signal at U414 pin 5 is correct.

## Initialization:

DISCON = 01100000. Significant bits are b2, b5, b6, and b7  $\overline{\text{(STOPDIS}}$ , enable "Q" bus, not ENV mode).

MODECON = 00001000. Significant bit is b3 (U140 lower half).

MISC = 00100000. Significant bit is b5 (ZAXIS OFF).

The test result = PASS.

The test is to load a pattern into the display counters, U220 and U211, with the LDCOUNT strobe (data loaded to U222 is fixed). Their outputs are selected by U221, U212, U210 holding U414A in the reset mode and not PRESTART. Since the STOPDIS line is LO, the display counters are selected as the source to the Q bus (U210, U212, U221). The inputs to U130 are the bits Q1..Q5 where Q1..Q3 = 0. and Q4, Q5 are the b0, b1 data of pattern. To read back properly, shift the pattern left 3 bits and use only the lower 5 bits of XDIAG (U243).

- Test 1. 10100101 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 2., 01001011 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 3. 10010110 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 4. 00101101 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

Troubleshooting Procedure:

#### NOTE

Q0 through Q3 = 0. Q4 through Q11 map to D0 through D7; i.e., Q4 = d3. By knowing which test FAILs and the bit pattern one may easily determine the problem bit(s) (look for the bit column in the failed tests that are the same).

If 2 or 3 tests fail, then there is a bus problem of some sort and they must be examined. If all four tests FAIL, then the problem can be in several locations.

- 1. LDCOUNT might not be strobing the data into Display Counters U220 and/or U211 (schematic diagram 17).

- 2. U414A may not be resetting, or U323 pin 3 might be HI due to a failure.

- 3. Address Multiplexers U221, U212, and U210 may not be operating properly.

- 4. Ramp Buffer U130 (schematic diagram 16) may be defective.

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 1. Run test 2230 in CONTINUOUS mode and verify the LDCOUNT strobe pulse at pin 11 of U222, U220, and U211.

- Verify that after LDCOUNT strobe, that the outputs of U222, U220, and U211 are stable and of the correct level for the test selected.

- 3. Verify that U323 pin 3 is LO.

- Verify the outputs of U221, U212, and U210 are stable and correct after the LDCOUNT strobe to the previous bus.

- 5. Verify the chip enable to U130 pins 1 and 15 is LO. If ok to here, replace U130.

2340 U140 Readout Buffer U140 (diagram 16):

Testing Method:

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2341 to 2344.

This test requires the display state machine to be operative. There is no "good" way to insure that it is functional and there have been no previous tests. Therefore, if this test fails, it could be for several reasons other than U140.

# Initialization:

DISCON = 01100000. Significant bits are b2, b5, b6, and b7 (STOPDIS, enable "Q" bus, not ENVELOPE mode).

MODECON = 00001000. Significant bit is b3 (U140 lower half).

MISC = 00100000. Significant bit is b5 (ZAXIS OFF).

The test result = PASS.

The test is to load a pattern into the display counters, U220 and U211, with the LDCOUNT strobe. The counter-outputs are switched to the Q bus through U221, U212, U210 by holding U414A in the reset mode (PRESTART + DISPLAY is LO). The inputs to U140 (lower half) are the bits Q6 through Q8 where Q1 through Q3 = 0. Q4 and Q5 are the b0 and b1 data of the pattern. To read back properly, one shifts the pattern left 3 bits and use bits 4, 5, and 6 of XDIAG (U243); the test result is set to FAIL if the test fails.

- Test 1. 10100101 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 2. 01001011 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 3. 10010110 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 4. 00101101 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Then MODECON is set to 00010000 to select the top half of U140 and the pattern is shifted left 2 bits. YDIAG (U141) bits 4, 5, 6, and 7 are tested, and the test result is set to FAIL if the test fails.

- Test 1. 10100101 is loaded and read back via U141. Test result is set to FAIL if not a match on bits 0 through 5.

- Test 2. 01001011 is loaded and read back via U141. Test result is set to FAIL if not a match on bits 0 through 5.

- Test 3. 10010110 is loaded and read back via U141. Test result is set to FAIL if not a match on bits 0 through 5.

- Test 4. 00101101 is loaded and read back via U141. Test result is set to FAIL if not a match on bits 0 through 5.

#### NOTE

Q0 through Q4 = 0. Q4 through Q11 map to D0 to D7. i.e., Q7 = D3. By knowing which test FAILs and the bit pattern one may easily determine the problem bit(s) (look for the bit column in the failed tests that are the same).

If 2 or 3 tests fail, then there is a bus problem of some sort, and the busses must be examined. If all four tests FAIL, then the problem can be in several locations.

- 1. LDCOUNT might not be strobing the data into U220 and/or U211 (Display Counters, schematic diagram 17).

- 2. Flip-flop U414A may not be resetting, or OR-gate U323 pin 3 might be HI due to a failure.

- 3. The busses into or out of Address Multiplexers U221, U212, U210 may not be operating properly.

- 4. Readout Buffer U140 may be defective.

Troubleshooting Procedure:

Set up the 2430 test scope as in Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 1. Run test 2340 and verify the LDCOUNT strobe pulse at pin 11 of U222, U220, and U211.

- 2. Verify that after LDCOUNT strobe, that the outputs of Address Multiplexers U222, U220, U211 are stable and of the correct level for the test selected.

- 3. Verify that U323 pin 3 is LO.

- 4. Verify the outputs of U221, U212, and U210 are stable and correct after the LDCOUNT strobe to the previous bus.

- 5a. Verify the  $\overline{RO}$  chip enable to U140 pin 1 is HI for about half of the Trigger strobe positive period, and then that it goes LO and stays LO for the remaining time. This LO selects inputs Q6 through Q9 of U140.

- 5b. Verify the COUNTEN chip enable to U140 pin 19 has a HI-to-LO transition; then, before the time that U140 pin 1 goes LO, U140 pin 19 goes HI. While U140 pin 19 is LO, inputs Q6, Q7, Q8 are selected. If ok to here, replace U140.

#### 2350 U240

Readout Buffer U240 (diagram 16):

Testing Method:

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2351 to 2354.

This test requires the display state machine to be operative. There is no "good" way to insure that it is functional, and there have been no previous tests to help find that out. Therefore, if this test fails, it could be for several reasons other than U240.

#### Initialization:

DISCON = 01100000. Significant bits are b2, b5, b6, and b7 (STOPDIS, enable "Q" bus, not ENV mode).

MODECON = 00010000. Significant bit is b3 (U240).

MISC = 00100000. Significant bit is b5 (ZAXIS OFF).

The test result = PASS.

The test is to load a pattern into the display counters, U220 and U211, with the LDCOUNT strobe. The counter outputs are switched to the Q bus through U221, U212, U210 by holding U414A in the reset mode (PRESTART + DISPLAY is LO). The inputs to U240 are the bits Q0 through Q5 where Q0 through Q3 = 0. Q4 and Q5 are the b0, b1 data of pattern. To read back properly, one shifts the pattern left 6 bits and uses bits 6 and 7 of XDIAG (U243); the test result is set to FAIL if the test fails.

- Test 1. 10100101 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 2. 01001011 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 3. 10010110 is loaded and read back via U243. Test result is set to fail if not a match on bits 0 through 5.

- Test 4. 00101101 is loaded and read back via U243. Test result is set to FAIL if not a match on bits 0 through 5.

#### NOTE

Q0 through Q3 = 0, and Q4 through Q11 map to D0 to D7. i.e., Q7 = D3. By knowing which test FAILs and the bit pattern, one may easily determine the problem bit(s) (look for the bit column in the failed tests that are the same).

If 2 or 3 tests fail, then there is a bus problem of some sort that must be examined. If all four tests FAIL, then the problem can be in several locations.

- 1. LDCOUNT might not be strobing the data into U220 and/or U211.

- 2. Flip-flop U414A may not be resetting, or U323 pin 3 might be HI due to a failure.

- 3. Address Multiplexers U221, U212, and U210 may not be operating properly.

- 4. Readout Buffer U240 may be defective.

## Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 1. Run test 2350 in CONTINUOUS mode and verify the LDCOUNT strobe pulse at pin 11 of U222, U220, and U211.

- 2. Verify that after LDCOUNT strobe, the outputs of Address Multiplexers U222, U220, U211 are stable and of the correct level for the test selected.

- Verify that U323A pin 3 is LO.

- 4. Verify the outputs of U221, U212, and U210 are stable and correct after the LDCOUNT strobe to the previous bus.

- 5. Verify the RO chip enable to U240 pins 1 and 15 is LO. If ok to here, replace U240.

#### 2360 U322

Vertical Buffer U322 (diagram 16):

#### Testing Method:

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2361 to 2364. The contents of the first four bytes of U322 have been written and will now be tested against the values that were thought to be written, any failure to match will cause that test to fail. U322 is decoded by reading address 2000h.

Set test result = PASS.

If contents of 2000h not equal to 10100101, then test result = FAIL.

If contents of 2001h not equal to 01001011, then test result = FAIL.

If contents of 2002h not equal to 10010110, then test result = FAIL.

If contents of 2003h not equal to 00101101, then test result = FAIL.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Using the CH 2 probe:

- 1. Run test 2360 in CONTINUOUS mode and check U322 pin 19 for a negative strobe  $\overline{\text{YSEL}}$  at 10  $\mu\text{s}$  from the LO-to-HI transition of the trigger pulse. If not present, troubleshoot U323 and the inputs to it.

- 2. Check for activity on the WRD signal line of U322 (pin 1); if no activity, check for open back to A12U564 (schematic diagram 2).

- 3. Check that the data pattern for the test is correct at the input and output pins of U322. The data is stable during the YSEL strobe on pin 19, and the data bit level must be read in coincidence with it as other activity is also taking place on the WD bus. A Word Recognizer probe would be useful to make these checks, but it is not necessary.

- 4. If the input and output data patterns of U322 do not match, replace U322. If they match each other, but are not correct, suspect a problem with Vertical RAM U431. Run test 2361 through test 2364 to see if all patterns fail. If all do not fail, troubleshoot for a bad bit of the failing test or tests.

- 5. Check pin 20 (DEY) and pin 18 (CSY) of U431 for a negative strobe coincident with the YSEL strobe. If either is not present, troubleshoot U421 and the input signals to it.

- 6. Check that pin 21 of U431 (WE) is HI during the HI portion of the trigger strobe (displayed on CH 1 of the test scope). The data writes of the test patterns occur during the LO portion of the trigger strobe, and that activity can be seen. If the WE signal is not correct, troubleshoot U422 and the input signals to it.

- 7. Replace U431.

### 2370 U314

Horizontal Buffer (diagram 16):

Testing Method:

If run from this level, all four tests are selected in turn, or one may execute any one test by selecting 2371 to 2374. The contents of the first four bytes of U314 have been written and will now be tested against the values that were thought to be written, any failure to match will cause that test to fail. U314 is decoded by reading address 2800h.

Set test result = PASS.

If contents of 2800h not equal to 10100101, then test result = FAIL.

If contents of 2801h not equal to 01001011, then test result = FAIL.

If contents of 2802h not equal to 10010110, then test result = FAIL,

If contents of 2803h not equal to 00101101, then test result = FAIL.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

#### Using the CH 2 probe:

- 1. Run test 2370 in CONTINUOUS mode and check U314 pin 19 for a negative strobe  $\overline{\text{XSEL}}$  at 10  $\mu\text{s}$  from the LO-to-HI transition of the trigger pulse. If not present, troubleshoot U323 and the inputs to it.

- 2. Check for activity on the WRD signal line of U314 (pin 1); if no activity, check for open back to A12U564 (schematic diagram 2).

- 3. Check that the data pattern for the test is correct at the input and output pins of U314. The data is stable during the XSEL strobe on pin 19, and the data bit level must be read in coincidence with it, as other activity is also taking place on the WD bus.

- 4. If the input and output data patterns of U314 do not match, replace U314. If they match each other, but are not correct, suspect a problem with Horizontal RAM U431. Run test 2371 through test 2374 to see if all patterns fail. If all do not fail, troubleshoot-for a bad bit of the failing test or tests. A Word Recognizer probe would be useful for making these checks but is not necessary.

- 5. Check pin 20 (DEX) and pin 18 (CSX) of U440 for a negative strobe coincident with the XSEL strobe. If either is not present, troubleshoot U421 and the input signals to it.

- 6. Check that pin 21 of U440 (WE) is HI during the HI portion of the trigger strobe (displayed on CH 1 of the test scope). The data writes of the test patterns occur during the LO portion of the trigger strobe, and that activity can be seen. If the WE signal is not correct, troubleshoot U422 and the input signals to it.

- 7. Replace U440.

#### 2400 TB-DSP

Running the test at this level will execute the Time Base Controller (U670) tests for Short-Pipe (SISO) and FISO modes.

The test causes Time Base Controller U670 to simulate all the necessary states to get an acquisition in Short-Pipe and FISO modes.

### 2410 U670 FISO

Time Base Controller A11U670 (schematic diagram 8):

Running the test executes the Time Base Controller in FISO mode.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Now using the CH 2 probe:

- 1. Run test 2410 in the CONTINUOUS mode. Set the Sec/Div setting of the test scope to 1  $\mu$ s and connect the CH 2 probe to pin 19 of bidirectional buffer U641 (TBSEL); save CH 2 into REF1 and Display REF1.

- 2. Position CH 2 down to allow room and connect the CH 2 probe to U641 pin 1; save CH 2 into REF2 and Display REF2. The LO TBSEL pulse should be coincident to a HI RD pulse; if not, then troubleshoot the TBSEL or the RD signal line.

- 3. Position CH 2 down to allow room to display the signal and probe U641 pin 11 through 18. While the REF1 signal TBSEL is LO and REF2 signal RD is HI, compare the results to 01100101 where U641 pin 11 is D7 and U641 pin 18 is D0. If they do not compare, replace U641.

- 4. Test the output of U670 pin 26 for a square wave with a period of about 200  $\mu$ s. If not correct, replace U670.

- 5. If present, test for the square wave at U680 pin 16; replace U680 if TIMER signal is missing.

- 6. If all checks were ok, suspect A12U542 (schematic diagram 2).

## 2420 U670 SISO

Time Base Controller A11U670 (schematic diagram 8):

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure and run test 2420 in the CONTINUOUS mode on the scope under test.

Now using the CH 2 probe:

- Position the trigger strobe (CH1) near the top of the crt and connect the CH 2 probe to pin 19, TBSEL, of U641. Adjust the Sec/Div setting of the test scope to 1 μs. Verify that there is a negative TBSEL pulse during the positive trigger strobe. Save the CH 2 waveform in REF1 and display REF1.

- Position the CH 2 display down to allow room and connect the CH 2 probe to U641 pin 1. Save CH 2 into REF2 and display REF2. The TBSEL pulse should be coincident to a HI RD pulse; if not, then troubleshoot the chip select or RD signal line.

- Position the CH 2 display down to allow room and probe U641 pin 11 through 18 while REF1 signal is LO and REF2 signal is HI. Compare the results to 01000000 where U641 pin 11 is D7 and U641 pin 18 is D0. If they do not compare, replace U641.

- 4. Test the output of U670 at pin 26 for a square wave signal (TIMER) with a period of about 200  $\mu$ s; if not present, replace U670.

- If present, test for the square wave at U680 pin 16 and replace U680 if missing.

- 6. If all checks were ok, suspect A12U542 (schematic diagram 2).

### 2500 MAIN

The MAIN board has five shift-register tests. These are in two groups. The first group includes Gate Array U270, Peak-Detector U530, Attenuators U511 and U221 (acting as one 16-bit register), Trig U140. The second group has the System-DAC U850 and U851 (acting as one 16-bit register).

From this level, the initialization and all five tests are selected in turn. An individual test may be run by selecting test numbers 2510 to 2560.

There is one diagnostic bit for readout off the main board and that is the logic-AND of the MSB of all the shift registers. The shift registers are preset to 10100101, or 1010010110100101 and the diagnostic bit is tested to see if a "1" is being read out for the MSB. If the diagnostic bit is not = 1, then either one of the registers is not loading or the diagnostic bit is stuck. In any event, no further meaningful data is possible, so the test stops. If initialization is successful, each bit is shifted out, register by register, and compared against what it should be by shifting the initial pattern and comparing the MSB. After any register is tested, it is reinitialized so the next register may be tested. Discon (input = U531 pin 18, output = U531 pin 17) is the diagnostic bit from the main board.

## 2510 INIT SHIFT REGS

Acquisition Control Shift Registers A10U270 (Gate Array), A10U530 (Peak Detector), A10U140 (Trig Control), DAC Input Shift Register A10U850/U851 (schematic diagram 5), and Attenuator Shift Register A10U221/U511 (schematic diagram 9):

Testing Method:

For this test to pass, the MSB of the five output registers above must be high. If one of the registers didn't have the correct pattern strobed in, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Run test 2510 in CONTINUOUS mode.

Using the CH 2 probe:

- Check A10U380 pin 3 (schematic diagram 5) for a HI level during the HI period of the trigger strobe. If ok, then check for the same signal at A11U531 pin 18 (schematic diagram 17). If correct and test is failing, replace U531 and run SELF DIAG.

- Check U380 pins 1 and 2. If both are HI during the trigger strobe HI and pin 3 does not follow, then replace U380. If neither pin 1 nor 2 is HI, then suspect DAC Select Multiplexer U272 or its input gating.

- 3. If U380 pin 2 is LO, then run test 2560 and troubleshoot using the procedure given for that number.

- 4. If U380A pin 1 is LO, then find which cathode of the input diodes (CR185, CR186, CR286, or CR287) is LO. Run the test number for the suspected Shift Register and check the inputs (clocks, data, and power) to it (look at the information given with the test number for the troubleshooting procedure for each Shift Register). If they are all ok, replace the suspected Shift Register; if not, troubleshoot the bad input.

## 2520 ATTEN

Attenuator Shift Registers A10U221/A10U511 (schematic diagram 9):

Testing Method:

For this test, the MSB of A10U511 (pin 13) will be compared with what the MSB should be with each shift of the register. If one of the bits differs from the loaded-in pattern, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

### NOTE

For the following, set the Trigger Position of the test 2430A to 3/4. If using an analog scope for testing, use the appropriate holdoff and trigger level to view the signals of interest.

Run test 2520 in CONTINUOUS mode. Using the CH 2 probe:

- 1. Check U511 pin 9 and U221 pin 9 for +5 V (registers not held reset). If not +5 V, then repair.

- Check Shift Register U221 at pin 8 for activity (ATT SR CLOCK line). If clock is missing, troubleshoot Control Register Clock Decoder A10U271 (diagram 5).

- 3. Check U221 pins 1 and 2 for activity (ACD line is the data input). If ACD missing, troubleshoot the signal path to and gating on the inputs of DAC Multiplexer Select register U272 (diagram 5).

- 4. Check U221 pin 13 for activity; replace U221 if inactive.

- 5. If checks good to this point and the test still fails, replace U511.

### 2530 PEAK DETECTOR

Acquisition Control Register A10U530 (schematic diagram 5):

Testing Method:

For this test, the MSB of A10U530 (pin 13) will be compared with what the MSB should be with each shift of the register. If one of the bits differs from the loaded-in pattern, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

#### NOTE

For the following, set the Trigger Position of the test scope to 3/4. If using an analog scope for testing, use the appropriate holdoff and trigger level to view the signals of interest.

Run test 2530 in CONTINUOUS mode. Using the CH 2 probe:

- 1. Check U530 pin 9 for a HI level. If LO, then check R531 and source of +5 V.

- 2. Check U530 pin 8 for activity (PD SR CLK signal line); if inactive, repair.

- 3. Check U530 pins 1 and 2 for activity (ACD line is the data input). Repair if inactive.

- 4. If all inputs are good, replace U530.

#### 2540 GATE ARRAY

Acquisition Control Register A10U270 (schematic diagram 5):

Testing Method:

For this test, the MSB of U270 (pin 13) will be compared with what the MSB should be with each shift of the register. If one of the bits differs from the loaded-in pattern, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2100 troubleshooting procedure.

#### NOTE

For the following, set the Trigger Position of the test 2430A to 3/4. If using an analog scope for testing, use the appropriate holdoff and trigger level to view the signals of interest.

Run test 2540 in CONTINUOUS mode. Using the CH 2 probe:

- 1. Check U270 pin 9 for a HI level. If not +5 V, check R269 and source of the +5 V.

- 2. Check U270 pin 8 for activity (GA SR CLK signal line); if inactive, repair.

- 3. Check U270 pins 1 and 2 for activity (ACD line is the data input). Repair if inactive.

- 4. If all inputs are good, replace U270.

2550 TRIG Acquisition Control Register A10U140 (schematic diagram 5):

Testing Method:

For this test, the MSB of A10U140 (pin 13) will be compared with what the MSB should be with each shift of the register. If one of the bits differs from the loaded-in pattern, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

### NOTE

For the following, set the Trigger Position of the test 2440 to 3/4. If using an analog scope for testing, use the appropriate holdoff and trigger level to view the signals of interest.

Run test 2550 in CONTINUOUS mode. Using the CH 2 probe:

- Check U140 pin 9 for a HI level (RESET). If LO, repair.

- 2. Check U140 pin 8 for activity (TRIG CONT CLK line). If inactive, repair.

- 3. Check U140 pins 1 and 2 for activity (ACD line is the data input); repair if inactive.

- 4. If all inputs are good, replace U140.

## 2560 SYSTEM DAC

DAC Input Shift Registers A10U850/A10U851 (schematic diagram 5):

Testing Method:

For this test, the MSB of A10U851 (pin 13) will be compared with what the MSB should be with each shift of the register. If one of the bits differs from the loaded-in pattern, the test fails.

Troubleshooting Procedure:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

#### NOTE

For the following, set the Trigger Position of the test 2440 to 3/4. If using an analog scope for testing, use the appropriate holdoff and trigger level to view the signals of interest.

Run test 2560 in the CONTINUOUS mode. Using the CH 2 probe:

- 1. Check U850 pin 9 and U851 pin 9 for HI level. If not +5 V, check R850 and source of the +5 V.

- 2. Check U850 pin 8 and U851 pin 8 for clock activity. If clocks are inactive, then:

- a. Check U280B pin 5 to have a LO gate present; replace U272 if pin 5 is stuck either HI or LO.

- b. Check U280B pin 6 for clocking signals during the HI period of the trigger strobe.

- c. Replace U280 if not gating correctly; troubleshoot clock signals if not present.

- Check the data input to U850 at pins 1 and 2. The signal should be a train of pulses during the HI period of the trigger strobe. If the data input signal is not present, test signals around U280D and correct.

- 4. Check U850 pin 13 that the first 8-bits of the 16-bit pattern comes out as the second is shifted into U850 at pins 1 and 2. (A Sec/Div setting of 0.5 ms on the test scope is good for viewing the data pattern, and the latched data on pin 13 is much easier to view than the input data pulses). If the data is not shifting through U850, then replace U850.

- 5. If the data is coming through U850, check U851 pins 1 and 2 to verify that it is ok there. Check pin 13 of U851 for a data pattern of 1010010110100101. (Each bit is approximately 0.2 ms wide, so a 0.4 ms wide pulse is two bits.)

- 6. Replace U851 if not shifting the signal through.

#### 2600 SIDE U761/U762

Holdoff Register A11U762 (schematic diagram 13):

### Testing Method:

From this level, all four tests are selected in turn. Individual test may be called by selecting test numbers 2610 to 2640. The test involves writing 4 unique patterns to U762 and reading them back from U761. The four patterns test for all stuck-at(s) and for lines shorted to other lines. By knowing which test FAILs and the bit pattern, one may easily determine a bus problem by observing which bits are the same in the failed tests.

The HOREG register is two integrated circuits; U762 is a latch and the read back is U761. If all tests pass, the test result is set to PASS; any failure sets it to FAIL.

#### NOTE

Bit 3 of the test patterns is not allowed to be set LO as it would reset the GPIB chip and we cannot restart it from the diagnostic routines.

- Test 1. 10101101 is sent to U762 and read back via U761. Test result is set to FAIL if not a match.

- Test 2. 01001011 is sent to U762 and read back via U761. Test result is set to FAIL if not a match.

- Test 3. 10011110 is sent to U762 and read back via U761. Test result is set to FAIL if not a match.

- Test 4. 00101101 is sent to U762 and read back via U761. Test result is set to FAIL if not a match.

Troubleshooting Procedure:

If the failure occurs for all tests:

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Now using CH2 probe:

- 1. Check that U762 pin 1  $\overline{\text{HOREG}}$  is LO about 12  $\mu$ s after the trigger strobe. If  $\overline{\text{HOREG}}$  is absent, test the inputs of U781. Replace U781 if the inputs are ok; if not ok, troubleshoot that problem.

- Check that U762 pin 9 (WR clock) has a LO-to-HI transition during the enable time. (Save enable in REF1 and display it while looking at the clock.) Clock line is the write line; if missing, suspect open run or connection.

- 3. Check the outputs U762 (pins 15, 12, 10, 7, and 5) for the proper levels for the pattern that is being looped on. Replace U762 if incorrect.

- 4. Check U761 pin 1 to be enabled after the clock to U762 pin 9. If present, then the problem is possibly U762.

## 3000 SYS-RAM

All RAM tests are non-destructive. The Display RAM is tested first, and, if found good, the contents of the other RAMs are stored in the Display RAM as they are tested. The contents are returned after the test is complete.

From this level (3000), all eight RAM tests are selected in turn. An individual RAM test may be run by selecting test levels 3100 to 3800.

#### NOTE

An internal jumper, A13J156, must be removed before test levels 3700 and 3800 may be run. If the jumper is removed and test levels 3700 and 3800 are run, loss of power during while they are running can result in loss of internal calibration constants. In that event, a partial recalibration is required (see information regarding power loss while running SELF CAL under "Diagnostics" in this section). Run these tests only if necessary.

| 3100 A11U431 |         | 3500 A11U600 |

|--------------|---------|--------------|

| 3200 A11U440 |         | 3600 A12U440 |

| 3300 A12U350 | <br>4 2 | 3700 A12U664 |

| 3400 A11U430 | <br>    | 3800 A12U664 |

Each RAM test (levels 3100-3800) is comprised of the four following subparts:

A logic one is shifted left through a field of logic zeros while incrementing the address (the "-" TRIGGER SLOPE LED is lit).

A logic one is shifted right through a field of logic zeros while decrementing the address (the "+" TRIGGER SLOPE LED is lit).

A logic zero is shifted left through a field of logic ones while incrementing address (the "-" TRIGGER SLOPE LED is lit).

A logic zero is shifted right through a field of zeroes while decrementing the address (the "+" TRIGGER SLOPE LED is lit).

Running level 3000 causes all four parts of the test to be performed on all 8 RAMs (sublevels 3100-3800), while running an individual sublevel test causes the four-part test to be performed on the corresponding RAM device.

Running a sublevel test from  $3\times10$  to  $3\times40$  (where  $\times=1-8$ ) runs the part (out of four parts) indicated by the test label (for instance, "3340 1-0S" runs the test that shifts logic 0 left in a field of logic ones for an incrementing address on U350).

### 3100 A11U431

# RAM A11U431 (schematic diagram 16):

Troubleshooting Procedure:

If test = FAIL then look for failure and correct using the following steps:

Using the CH 1 probe:

Run test 3110 in CONTINUOUS mode and check for activity on the chip select line to U431 (CSY, pin 18). If active, trigger the test scope on the signal. If no chip select, work backwards and find problem.

Using the CH 2 probe:

- 2. Check for activity on the write enable line to U431 (WE, pin 21) and note that it is LO at the same time as the chip select line. If no signal present, work backwards and find the problem.

- 3. Check for activity on the output enable line to U431 (DEY, pin 20). If none, work backwards and find the problem.

- 4. Check the data I/O pins of U431 (pins 9, 10, 11, 13, 14, 15, 16, and 17) for activity when test 3100 is selected. If no activity when DEY (output enable) is LO (pin stuck HI or LO), then suspect U322; otherwise suspect U431.

## 3200 A11U440

# RAM A11U440 (schematic diagram 16):

Troubleshooting Procedure:

If test = FAIL then look for failure and correct using the following steps:

Run test 3210 in CONTINUOUS mode.

Using the CH 1 probe:

Check for activity on the chip select line U440 (CSX, pin 18, and trigger the scope on the CH 1 signal. If none, work backwards and find problem.

## Using the CH 2 probe:

- 2. Check for activity on the write enable line U440 pin 21, and note that it is LO at the same time as the chip select line. If none, work backwards and find the problem.

- 3. Check for activity on the output enable line U440 pin 20. If none, work backwards and find the problem.

- Check the data I/O pins U440 (pin 9, 10, 11, 13, 14, 15, 16, and 17) for activity when test 3210 is selected. If no activity (stuck HI or LO) when output enable is LO, then suspect U314; otherwise suspect U440.

## 3300 A12U350

# RAM A12U350 (schematic diagram 2):

Troubleshooting Procedure:

If test = FAIL then look for failure and correct, using the following steps:

Select test 3310 and RUN CONTINUOUSLY.

#### Using the CH 1 probe:

- Check for activity on the pin 20 chip select line to U350, and trigger the scope on the signal if active. If no chip select, work backwards through the chip select circuitry and find problem.

- 2. Check for activity on the write enable line to U350 (WRR, pin 27) and note that it is LO at the same time as the chip select line. If no activity, work backwards and find the problem.

- 3. Check for activity on the output enable line to U350 (WRD, pin 22). If no activity, work backwards and find the problem.

- Check the data I/O pins U350 (pins 9, 10, 11, 13, 14, 15, 16, and 17) for activity when test 3400 is selected. If no activity (stuck HI or LO) when output enable is LO, then suspect buffer U352; otherwise suspect U350.

## 3400 A11U430

RAM A11U430 (schematic diagram 16):

Troubleshooting Procedure:

If test = FAIL then look for failure and correct using the following steps:

Run test 3410 in CONTINUOUS mode.

Using CH 1 probe:

1. Check the write enable to U430 (WRA, pin 8) for activity and trigger on the signal if active. If no activity, troubleshoot OR-gate U422A and U422C and their input signals. Check that pin 10 is LO; if not, repair.

Using the CH 2 probe:

- 2. Check for activity at the data input to U430 (DI, pin 11) timed with the enable pulse. If no signal, suspect U423A or U422B.

- If the checks in Steps 1 and 2 are ok, replace U430.

## 3500 A11U600

ACQUIRE RAM A11U600 (schematic diagram 8):

Troubleshooting Procedure:

If test = FAIL then look for failure and correct, using the following steps:

Run test 3510 in CONTINUOUS mode.

- Check for LO on chip select line U600 pin 18. Repair if not LO.

- 2. Check for activity on the write enable line to U600 (WE, pin 21). If no activity, work backwards and find the problem.

- Check for activity on the output enable line to U600 (OE, pin 20). If no activity, work backwards and find the problem.

- Check the data I/O pins of U600 (pins 9, 10, 11, 13, 14, 15, 16, and 17) for activity when test 3500 is selected. If no activity (stuck HI or LO) when the output enable is LO, then suspect buffer U610; otherwise suspect U600.

- 5. Check the address lines (MA0-MAA) for activity. If no activity on any lines, troubleshoot the WE and TB2MEM signals to U300, U400, and U410. If an address line is stuck, troubleshoot that problem.

## 3600 A12U440

CMD/TMP RAM A12U440 (schematic diagram 2):

NOTE

If tests 3300 through 3600 all fail, the most likely faults are: a stuck data line to A12U352, a bad select signal to A12U352, or Waveform Data Buffer A12U352 itself.

Troubleshooting Procedure:

If test = FAIL then look for failure and correct, using the following steps:

Run test 3610 in the CONTINUOUS mode.

Using the CH 1 probe:

Check for activity on the chip select line to A12U440 (pin 20), and trigger the scope on the signal if active. If no activity, work backwards through U250C and find the problem.

Using the CH 2 probe:

2. Check the data I/O pins of U440 (pins 11, 12, 13, 15, 16, 17, 18, and 19) for activity. If no activity when output enable is LO, then suspect U440; otherwise check U352.

3700 or 3800 A12U664 A12U664 (schematic diagram 2)

#### NOTE

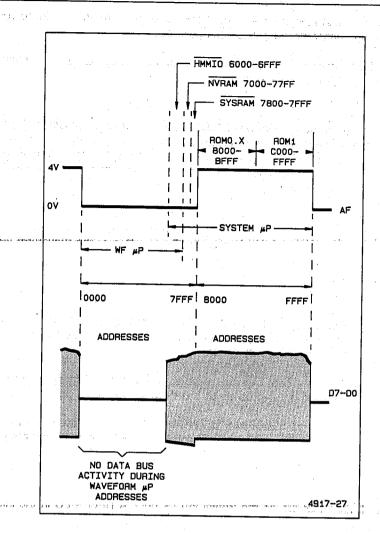

The test of RAM device A12U644 is divided into two test levels, 3700 and 3800. The sections of U644 that may be accessed depends on the condition of the BUSREQ output of A12U860. With BUSREQ set HI, the 8K×8 memory space corresponding to addresses 7000H to 8FFFH is the only space available; with BUSREQ set LO, the 24K×8 memory space corresponding to addresses 0000H to 5FFFH are both available. Level 3700 tests the 7000H to 8FFFH block while level 3800 tests the 0000H-5FFF block resulting in the entire 32K×8 RAM being tested. The Troubleshooting Procedure that follows applies to both test levels.

## Troubleshooting Procedure:

#### NOTE

If the System Ram data bus, chip selects, or output enable lines are defective, the System  $\mu P$  cannot run the the diagnostics testing. Therefore, if test 3700/3800 fails, the most likely problem is U664. If the diagnostics tests do not run, the Kernel test will have to be used to isolate a system bus or address decoding problem. An NV RAM failure due to stored data being scrambled requires a "COLD START" to reload the NV RAM with correct nominal values. The COLD START should be followed by a SELF CAL and then an EXTENDED CAL of ATTEN, TRIGGERS, and REPET to return it to a completely calibrated state.

If test = FAIL, look for failure and correct using the following steps:

Run test 3710 or 3810 in CONTINUOUS mode.

Using the CH 1 probe:

Check for a LO on pin 20. If it is HI, check back to the source of the problem starting with Q960.

Check for a HI on chip select 2 (pin 26). If not HI, check back to the source of the problem start with U424A.

Using the CH 2 probe:

Check for activity on the write enable line pin 27.

Check for activity on the output enable line pin 22.

Check the data I/O pins (pins 11, 12, 11, 15, 16, 17, 18, 18) for activity.

Check the data I/O pins (pins 11, 12, 13, 14, 15, 16, 17, 18,) of U660 for activity. If not active, check its write enable and output enable lines (pins 1, 19).

4000 FPP

Front Panel  $\mu$ P A13U700 (schematic diagram 3):

### Testing Method:

The Front Panel Processor test first sets all test results to NULL. Any failure to complete all the tests will result in a locked front panel. Depending on the nature of the failure, the Trigger LEDS may be latched in the first number of the test level that failed, the failure code may be flashed out on the LEDS (if it is the first failed test), or it may make it through the diagnostic, but with the FPP test marked FAIL. That information will help to isolate which circuitry may be defective and gives the starting point in troubleshooting a failure. It will be necessary to turn off the scope and turn it back on again to repeat the diagnostic testing from the front panel; however, testing may be done using GPIB diagnostic test commands.

The Front Panel  $\mu P$  internal diagnostics require that the  $\mu P$  be reset. Therefore, the structure of the FPP tests is such that the processor is initialized when completed. This requires that ALL of the tests be run in order. Therefore, all tests will be run even though it appears that only a sub-test is being executed.

#### Test Steps:

- 4100 U861 pin 9 should be reset to its LO state via U862B and U862A.

- 4200 U861 pin 6 should be reset to its HI state via U862C and U862D.

- 4300 U861 pin 9 (WR TO HOST) should clock pin 9 HI.

- 4400 U700 (Front Panel  $\mu$ P) checks its internal RAM, ROM, Timer, and A/D. Any failure will set the test result to FAIL.

- 4500 U861 pin 6 (FPDNRD) should clock pin 6 LO.

- 4600 U742 and U751. Four bit patterns are written to the FPP and echoed back. If these are not returned properly, the test result = FAIL.

# Troubleshooting Procedure:

Failure of one of the Front-Panel  $\mu P$  tests may be indicated only by flashing out the failed test number on the Trigger LEDs, but if the diagnostic testing can continue past the failure, the Extended Diagnostic menu will be seen with the FPP test marked FAIL. The usual result of a Front Panel  $\mu P$  failure is a locked up front panel (the button and pots will not be functional). To rerun the diagnostic testing from the front panel to check the Trigger LEDs for the failed test number, it is necessary to turn off then turn back on the scope.

Troubleshooting Front-Panel μP A13U700:

- 1. Check pin 5 for the 4 MHz clock.

- 2. Check pin 4 for +5 V, pin 1 for ground.

- 3. Check pins 8, 14, 16, 17, 19, 31, and 32 for +5 V and pins 6, 7, and 20 for ground.

- 4. Perform the Front Panel  $\mu$ P test if all the checks in steps 1, 2, and 3 were ok. If not, troubleshoot any problem area found by the checks.

#### Front Panel µP Test:

- 1. Turn off power and short pins 1 and 2 of J155 together. (The pins must remain shorted together during power-on.) This places the Front-Panel  $\mu P$  in the continuous self-diagnostic mode (Test 4400). Connect a test scope to view the signal present on pin 14 of U700.

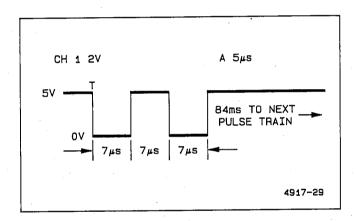

- 2. Turn the power back on and observe the signal at pin 14. See test waveform illustration of Figure 6-9 for correct waveshape and timing.

Figure 6-9. Front Panel  $\mu P$  diagnostics test.

3. If the test waveform is not present and the supply voltage, the ground, and the clock are correct, change the Front-Panel  $\mu$ P; it is possibly defective.

If the Front-Panel  $\mu P$  checks out ok, turn off the power and remove the jumper connected for the preceding Front Panel diagnostic test. Turn the scope back on and perform the following circuit checks for any of the Front Panel tests that failed when running the Extended Diagnostics via the GPIB. Use the circuit checks to isolate the problem in the associated circuitry. IF THE FPP DIAGNOSTICS TEST FAILED, THE ONLY WAY TO RUN THESE TESTS WILL BE VIA GPIB, AS THE FRONT PANEL WILL NOT RESPOND TO BUTTON PRESSES. To gain access to the scope via the GPIB when the EXT DIAG menu is being displayed, a MENU OFF command must be sent to exit extended diagnostics.

#### NOTE

Since the Front Panel  $\mu P$  is being reset in this test, there is no way to HALT if one chooses a CONTINUOUS loop mode and runs the tests from the front panel. However, to allow access to these features for any possible troubleshooting, looping has not been disabled. ONCE A TEST IS INVOKED IN CONTINUOUS MODE, A POWER OFF/ON CYCLE MUST BE USED TO EXIT FROM THE FRONT PANEL. Via the GPIB, the tests may be started and halted by sending the appropriate commands.

Set up the test scope as in Step 1 of the 2110 troubleshooting procedure.

Run tests 4100 through 4600 in CONTINUOUS mode. Use the CH 2 probe for the following checks while the specific test is selected and running.

### 4100 A13U861 pin 9 (FPINT):

- 1. Check U862 pin 1 for 0.2  $\mu$ s negative strobe during the HI period of the trigger strobe. If not present, replace U862.

- Check U861 pin 9 for a HI-to-LO transition. If not occurring, replace U861.

### 4200 A13U861 pin 6 (FPDNRD):

- Check U861 pin 1 for a negative strobe during the HI period of the trigger strobe. If not present, replace U862.

- Check U861 pin 6 for a LO-to-HI transition from the strobe at U861 pin 1. If occurring, replace U861.

# 4300 A13U700 pin 12 (WR TO HOST):

1. Check that U861 pin 9 has a HI pulse. If not, select 50 ms/div and ENVELOPE acquisition mode on the test scope; then, run test 4000 for the scope under test. At pin 12 of U700, check for a strobe occurring near the falling edge of the trigger strobe. If the strobe is ok, replace U861. If missing, test for 4 MHz at U700 pin 5 and replace U700 if the 4 MHz clock is ok.

If the 4 MHz clock is missing, troubleshoot the clock source. Restore the prior test scope setup as for test 2110 (a good use for the AUTOSTEP SEQUENCER).

# 4400 DIAG BYTE A13U700:

- 1. Check that the enable pulse to U751 (pins 1 and 19) is present and save to REF1. If not present, check for an open between U862A pin 1 and U751 pins 1 and 19.

- Display REF1 and probe U751 pin 18, 16, 14, and 12. These should all be LO during the time U751 is enabled. If not LO, it indicates either a problem in U700 or an invalid DC voltage level at one of the U700 inputs. If one of these four diagnostic bits is HI and the supply pins, etc., are ok, replace U700.

# 4500 A13U700 pin 13 (FPDNRD):

1. Select the 1/2 TRIG POSITION and set the Sec/Div setting to 1 ms on the test scope. Check for the FPDNRD clock pulse to U861 at pin 3 (leads the trigger strobe rising edge about 120  $\mu$ s). If missing, replace U700.

- 2. Check for LO at U861 pin 6; replace U861 if pin 6 is HI.

- 3. Check A12U654 pin 13 for LO. Replace A12U654 if pin 13 is LO and test is failing.

# 4600 A13U742/A13U751:

- 1. Check for a pattern of 10100101 at U742 pin 19, 16, 15, 12, 9, 6, 5, and 2 at the rising edge of the trigger strobe (Word Recognizer Probe is useful for this check). If not, and U742 pin 11 is LO, then replace U742. If U742 pin 11 is HI, replace U700.

- 2. Check the enable pulse at U751 pins 1 and 19. Save and move to REF1.

- 3. Display REF1 and check for a 10100101 pattern coincident with the enable pulse at U751 pins 17, 15, 13, 11, 8, 6, 4, and 2. If not ok, replace U700.

- Display REF1 and check for a 10100101 pattern coincident with the enable pulse at U751 pins 3, 6, 7, 9, 12, 14, 16, and 18. If not ok, replace U751.

### 4700 BATT STATUS

Battery A12BT800 (NVRAM keep-alive battery) (schematic diagram 1):

### Testing Method:

There is no hardware exercised for this test. The operating system is informed by the front panel processor if the battery voltage is either high or low. The "test" is to read a memory location where the System  $\mu P$  has stored the status after checking with the FPP. If the status is unknown, the result is NULL. If the test "passes," it means that it is not defective in that direction.

# Troubleshooting Procedure:

#### 4710 HIGH:

Either the voltage is really high or the detection circuitry is defective.

- Measure the battery voltage directly across the battery (BT800) and check for a range of 2.5 V to 3.7 V. If ok, then test from the + lead of BT800 to ground for the same or less voltage.

- If ok, test for the same voltage range at A13U700 pin 21. If ok there, replace A13U700. If voltage is wrong at pin 21, backtrack to the problem component (suspect A12U940).

- If the battery voltage is too high or the voltage to ground from the + lead is too high, check A12CR802. To ensure continued proper operation of the NVRAM, replace A12BT800 after correcting the overvoltage condition.

#### WARNING

When replacing the lithium battery, avoid personal injury by observing proper methods for handling and disposal. Improper handling may cause fire, explosion, or severe burns. Don't attempt to recharge and don't crush, disassemble, heat the battery above 212°F (100°C), incinerate, or expose contents of the battery to water. Dispose of battery in accordance with local, state, and national regulations.

#### 4720 LOW:

Either the battery is defective or the detecting circuit is defective.

- 1. Measure the battery voltage for a range of 2.4 V to 3.7 V. If low, replace the battery (BT800) observing the proper handling procedures.

- 2. If the battery voltage is correct, troubleshoot the detection circuitry as for a failure of test 4710, looking for the cause of a LOW reading.

## 5000 WP U470

Waveform μP A12U470 (schematic diagram 2):

Testing Method:

The nature of these tests is such that all tests must be executed in order and may not be individually executed. Therefore, any attempt to execute one test will result in all tests being executed.

The Waveform Processor test first sets all test results to NULL. Any failures will be fatal in terms of instrument operation; however, the last test that was executed will be set FAIL and should help in diagnosing the cause of the problem.

The Waveform  $\mu P$  command memory has been checked out by this time as well as the bus structure that permits the System  $\mu P$  to control the Waveform  $\mu P$  bus.

#### 5100 RUN-TASK

Testing Method:

Loads a task into Command Memory U440 and tells the Waveform  $\mu P$  to execute it. A 30 ms timeout is executed; and then, INTREG (bit 0) is tested for WPDN. If it has not been set, the task did not execute and terminate properly. If 5100 fails, it could be the Waveform Processor code ROMs, or the Waveform  $\mu P$  itself (U470). In any event, the Waveform Processor Kernel tests will need to be run to diagnose the source of the problem.

Troubleshooting Procedure:

Use the Waveform  $\mu P$  Kernel test in Procedure 8 to troubleshoot for a  $\mu P$  fault or a fault on the Waveform  $\mu P$  address or data bus.

## 5200 BUSGRANT

Testing Method:

This test executes a bus request by setting bit D5 (pin 14) of PCREG U860 (schematic diagram 1) HI, delaying 10 ms, and checking bit D6 of INTREG (Interrupt Register) U654 to see if a BUSGRANT has occurred.

Troubleshooting Procedure:

Set up the 2440 test scope as in Step 1 of the 2110 troubleshooting procedure.

Run test 5200 in CONTINUOUS mode. Using the CH 2 Probe:

- 1. Check U860 pin 15 for LO-to-HI transition. If not occurring, replace U860.

- 2. Check U332D (schematic diagram 2) pin 13 for LO-to-HI transition. If not occurring, replace Waveform  $\mu P$  U470.

- 3. Check U332D pin 11 for LO-to-HI transition. If not gating, replace OR-gate U332.

#### 5300 VERSION-CHK

Waveform  $\mu P$  ROM A12U480 and A12U490 (schematic diagram 2):

### Testing Method:

The version number in the header is preset to "?" and is filled in by this test. If the test fails, the "?" will remain in the header for further indication of an error. A Waveform  $\mu P$  reset causes the Waveform  $\mu P$  to read the version number bytes of the Waveform  $\mu P$  code. If the version number is incorrect, the Waveform  $\mu P$  code is incompatible with the System  $\mu P$  code and may not execute properly.

# Troubleshooting Procedure:

If test 5300 fails, replace Waveform  $\mu P$  ROMs U480 and/or U490 with the correct ones for the version of System  $\mu P$  code being used.

## 6000 CK SUM-NVRAM

Nonvolatile RAM Checksum A12U664 (schematic diagram 1):

# Testing Method:

Some of the CRCCs (check sums) are computed at power-down and will be valid only at power-up. Therefore, executing tests 5000 through 5003 will only display the flags that resulted from power-up diagnostics.

#### NOTE

FAIL and PASS flags in the Extended Diagnostics menu show the results of the last test ran. If a defective device that has previously caused a FAIL flag to be set is replaced, the test must be run again to obtain a PASS indication in the menu.

When the instrument is SELF CALIBRATED, a CRCC is calculated and stored for the Calibration Constants in NV RAM.

When power-down is executed, the values of the front-panel variables have a CRCC calculated and stored.

When a waveform is saved, the CRCC is calculated for the waveform and headers and saved.

On power-up, all of these are recalculated and compared to the stored CRCC word. If they do not agree, that test fails.

### 6100 CAL CONSTANTS

Calibration Constants:

Troubleshooting Procedure:

If FAIL, the calibration constants have been lost and a COLD START is executed. The instrument must be recalibrated to return to calibrated operation after a COLD START.

A failure of 6100 is serious to the normal operation of the scope, and the cause of the failure should be found and corrected to prevent reoccurrence.

Check BT800 and the components that connect and disconnect the battery from the NV RAM at power-off and power-on respectively.

#### WARNING

If replacing the lithium battery, avoid personal injury by observing proper methods for handling and disposal. Improper handling may cause fire, explosion, or severe burns. Don't attempt to recharge and don't crush, disassemble, heat the battery above 212°F (100°C), incinerate, or expose contents of the battery to water. Dispose of battery in accordance with local, state, and national regulations.

2. Test several times by cycling the power after the instrument has completed its self testing. If the test continues to fail, check the PWRUP line to U640 pin 2, and ensure that it is reset LO when the power line voltage drops below the minimum line voltage. If this line does not go LO soon enough, the power-down routines will not calculate the current check sums before the power is completely lost.

## 6200 . FP-LAST

Front Panel Control Settings:

Troubleshooting Procedure:

If the last front-panel setup has been lost, the instrument will be set up in the INIT PANEL configuration in the AutoStep Sequence menu (push PRGM).

If this event is due to a component failure, the RAM test, 3700 and/or 3800, or BATT-STATUS test 4700 should also have failed. Check NVRAM device U664 and associated circuitry or the Battery circuit as appropriate.

The reference waveform memories will be declared EMPTY if the WFM-HEADERS do not check correctly. These waveforms are stored in A12U350. Therefore, if the problem is due to failed components, the RAM test (3300) or BATT-STATUS (4700) should have failed.

## 6400 PRGM

State of the AutoStep Sequencer memory:

Testing Method:

Each time an AutoStep Sequence is modified, a CRCC (check sum) is calculated and stored. At power-up, a CRCC is calculated again and compared with the last value stored. If there is a discrepancy, the FAIL flag is set and all the pointers for the AutoStep Sequences are initialized so that the sequences are lost.

The most likely cause of a PRGM failure is a loss of power while memory is being reclaimed after a sequence has been deleted. If, rather, this event is due to a component failure, the RAM test, 3700 and/or 3800, or BATT-STATUS test 4700 should also have failed. Check NVRAM device U664 and associated circuitry or the Battery circuit as appropriate.

7000 CCD CCD/CLOCK DRIVERS A10U350 (CH 2) and A10U450 (CH 1) (schematic diagram 10):

Testing Method:

These tests, if passed, indicate that the hardware is functional.

IF A SELF DIAG OR EXTENDED DIAG TEST FAILS, ONE CANNOT ASSUME THE HARDWARE IS DEFECTIVE UNLESS THE SAME TEST FAILS A SELF CAL. The reason that SELF CAL must be run to assure a hardware failure is that SELF CAL computes new values of the constants for each test and uses them in the subsequent tests; whereas, diagnostic tests use previously stored constants for making the tests. If those stored values are not valid for the present operating temperature of the scope, the test may not be able to converge to a solution.

The CCD has two classes of adjustments, centering and gain. In addition, several CCD parameters are measured and stored for use in Dynamic Calibration. Centering must be performed in all four acquisition modes because of offset differences in the different paths. Gain is performed in Short-Pipeline and FISO modes.

Troubleshooting Procedure:

The CCDs are a good suspect if any of the 7000-series diagnostic tests failed. The Extended Diagnostics menu should be examined to determine if the problem is in only one or in both of the channels.

If both channels fail: